Page 39 - PEN Ebook May 2021

P. 39

SEMICONDUCTORS Semiconductors

Modeling of Switching

transients of the SiC

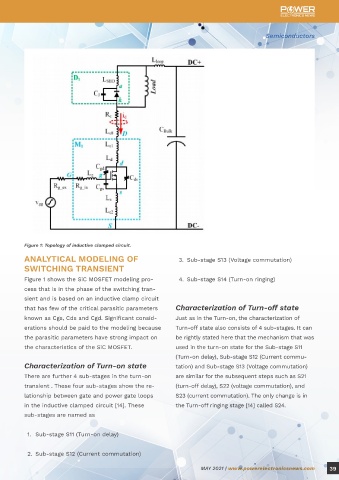

MOSFET Based on Finite Figure 1: Topology of inductive clamped circuit. 3. Sub-stage S13 (Voltage commutation)

ANALYTICAL MODELING OF

State Machine (FSM) SWITCHING TRANSIENT 4. Sub-stage S14 (Turn-on ringing)

Figure 1 shows the SiC MOSFET modeling pro-

cess that is in the phase of the switching tran-

By Maurizio Di Paolo Emilio, Editor-in-Chief of Power Electronics News and EEWeb sient and is based on an inductive clamp circuit

that has few of the critical parasitic parameters Characterization of Turn-off state

It has been observed in the areas of the aeronaut- simplicity in comparison with the physical and known as Cgs, Cds and Cgd. Significant consid- Just as in the Turn-on, the characterization of

ics, shipboard systems and electric vehicles, [1][2] spice modeling [6][7] respectively. erations should be paid to the modeling because Turn-off state also consists of 4 sub-stages. It can

[3] that one of the best solution available is the the parasitic parameters have strong impact on be rightly stated here that the mechanism that was

silicon carbide (SiC) MOSFET due to the high-fre- A huge number of models such as switching the characteristics of the SiC MOSFET. used in the turn-on state for the Sub-stage S11

quency HF and high-density of its converters. SiC transient, influences of parasitic parameters, (Turn-on delay), Sub-stage S12 (Current commu-

MOSFET offer faster switching along with lower switching loss, switching oscillation and high-fre- Characterization of Turn-on state tation) and Sub-stage S13 (Voltage commutation)

power loss as compared to the silicon Si based quency (HF) electromagnetic interference (EMI) There are further 4 sub-stages in the turn-on are similar for the subsequent steps such as S21

IGBT. This factor makes it able of operating with noise, [8][9][10][11][12][13] respectively have been transient . These four sub-stages show the re- (turn-off delay), S22 (voltage commutation), and

higher level switching frequency which is estimated given but none of them could be applied on lationship between gate and power gate loops S23 (current commutation). The only change is in

to be of several hundreds of kilo Hertz. That will switching loss. in the inductive clamped circuit [14]. These the Turn-off ringing stage [14] called S24.

eventually improve the charge density and efficien- sub-stages are named as

cy of the power converter [4][5]. This article will elaborate the analytical modeling

based on finite state machine (FSM) specifically 1. Sub-stage S11 (Turn-on delay)

Analytical modeling has the tendency of effec- for the evaluation of the switching characteristics

tively making the trade-off between accuracy and in terms of HF EMI noise and switching loss. 2. Sub-stage S12 (Current commutation)

38 MAY 2021 | www.powerelectronicsnews.com MAY 2021 | www.powerelectronicsnews.com 39