Page 77 - PEN eBook July 2023

P. 77

Semiconductors

The new SiC FETs take

advantage of Qorvo’s

exclusive cascode circuit

arrangement, in which a SiC

JFET is co-packaged with a

silicon MOSFET, to create a

device that fully leverages the

efficiency benefits promised

by wide-bandgap switch

technology and the easier gate

drive of silicon MOSFETs. SiC

JFETs provide the same R

DS(on)

as SiC MOSFETs but require

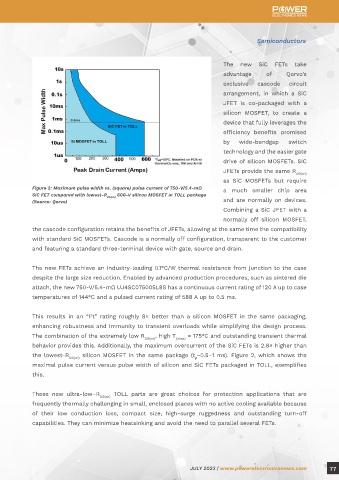

Figure 2: Maximum pulse width vs. (square) pulse current of 750-V/5.4-mΩ a much smaller chip area

SiC FET compared with lowest-R 600-V silicon MOSFET in TOLL package

DS(on)

(Source: Qorvo) and are normally on devices.

Combining a SiC JFET with a

normally off silicon MOSFET,

the cascode configuration retains the benefits of JFETs, allowing at the same time the compatibility

with standard SiC MOSFETs. Cascode is a normally off configuration, transparent to the customer

and featuring a standard three-terminal device with gate, source and drain.

The new FETs achieve an industry-leading 0.1°C/W thermal resistance from junction to the case

despite the large size reduction. Enabled by advanced production procedures, such as sintered die

attach, the new 750-V/5.4-mΩ UJ4SC075005L8S has a continuous current rating of 120 A up to case

temperatures of 144°C and a pulsed current rating of 588 A up to 0.5 ms.

This results in an “I t” rating roughly 8× better than a silicon MOSFET in the same packaging,

2

enhancing robustness and immunity to transient overloads while simplifying the design process.

The combination of the extremely low R , high T = 175°C and outstanding transient thermal

DS(on) j(max)

behavior provides this. Additionally, the maximum overcurrent of the SiC FETs is 2.8× higher than

the lowest-R silicon MOSFET in the same package (t ~0.5–1 ms). Figure 2, which shows the

DS(on) p

maximal pulse current versus pulse width of silicon and SiC FETs packaged in TOLL, exemplifies

this.

These new ultra-low–R TOLL parts are great choices for protection applications that are

DS(on)

frequently thermally challenging in small, enclosed places with no active cooling available because

of their low conduction loss, compact size, high-surge ruggedness and outstanding turn-off

capabilities. They can minimize heatsinking and avoid the need to parallel several FETs.

JULY 2023 | www.powerelectronicsnews.com 77