Page 53 - PEN Ebook May 2021

P. 53

Design Design

defined as junction temperatures. Thus, active Using the second equation from Table 1, the ac-

and passive mode do not require differentiation. celeration factor, and the second data point (45h)

There are certainly aging effects that are related of the mission profile in Table 2, the needed test

to current densities when an IC is operating, but time (tt) can be calculated with Equation (2):

these effects are minor when compared to the

aging effect of temperature.

Using the Arrhenius equation from Table 1, enter

the first data point (-40°C) of the mission profile

in Table 2. With a test temperature of 125°C, the

acceleration factor (Af) can be calculated with (2)

Equation (1):

That means the real-life stress represented by

-40°C over 45h would be equal to an HTOL test for

just a fraction of an hour at 125°C (see Table 2). In

(1) order to calculate the total mission profile stress,

all data points of the mission profile must be cal-

culated similarly, and the related equivalent test

times must sum to a total of about 5888h. That

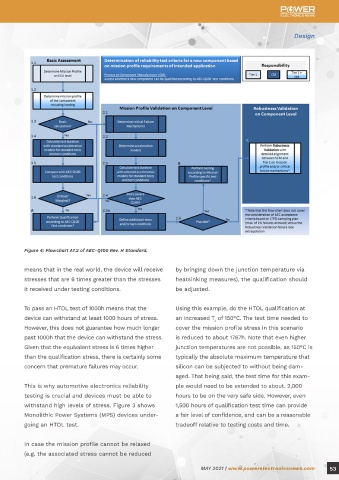

Figure 4: Flowchart A7.2 of AEC-Q100 Rev. H Standard.

means that in the real world, the device will receive by bringing down the junction temperature via

stresses that are 6 times greater than the stresses heatsinking measures), the qualification should

it received under testing conditions. be adjusted.

To pass an HTOL test of 1000h means that the Using this example, do the HTOL qualification at

device can withstand at least 1000 hours of stress. an increased T of 150°C. The test time needed to

J

However, this does not guarantee how much longer cover the mission profile stress in this scenario

past 1000h that the device can withstand the stress. is reduced to about 1767h. Note that even higher

Given that the equivalent stress is 6 times higher junction temperatures are not possible, as 150°C is

than the qualification stress, there is certainly some typically the absolute maximum temperature that

concern that premature failures may occur. silicon can be subjected to without being dam-

aged. That being said, the test time for this exam-

This is why automotive electronics reliability ple would need to be extended to about. 2,000

testing is crucial and devices must be able to hours to be on the very safe side. However, even

withstand high levels of stress. Figure 3 shows 1,500 hours of qualification test time can provide

Monolithic Power Systems (MPS) devices under- a fair level of confidence, and can be a reasonable

going an HTOL test. tradeoff relative to testing costs and time.

In case the mission profile cannot be relaxed

Figure 3: MPS Devices Under HTOL Test Operate Under Load Conditions. (e.g. the associated stress cannot be reduced

52 MAY 2021 | www.powerelectronicsnews.com MAY 2021 | www.powerelectronicsnews.com 53