Page 23 - EE Times Europe Magazine | February 2020

P. 23

EE|Times EUROPE 21

Optimized for Success

need for safety software — different safety

mechanisms can now be exercised through

hardware built-in self-tests.

Computing performance has been

increased with the introduction of the new

TriCore generation (1.62) with new instruc-

tions, up to six CPUs running at 300 MHz, as

well as reduced latencies with direct path for

flash access.

On the memory side, not only have

capacities been increased, but the memory

protection unit (MPU) has been further

improved.

The TC3xx family incorporates various

high-performance AD converters. Four types

of converters are integrated: primary SAR (12

bit), secondary SAR (12 bit), fast compare (10

bit), and delta-sigma. The converters offer

conversion rates from 1 to 40 MSamples/s.

The optimized ADAS functionality of the

AURI TC xx family benefits radar systems

in particular (Figure 4), from blind-spot

detection to front and corner radar systems.

The TC3xx offers the previously mentioned

radar-processing unit with up to two SPUs,

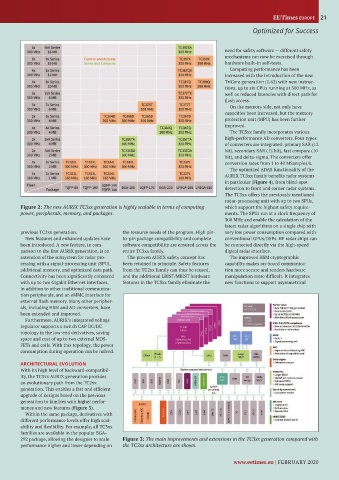

Figure 2: The new AURIX TC3xx generation is highly scalable in terms of computing which support the highest safety require-

power, peripherals, memory, and packages. ments. The SPUs run at a clock frequency of

300 MHz and enable the calculation of the

latest radar algorithms on a single chip with

previous TC2xx generation. the resource needs of the program. High pin- very low power consumption compared with

New features and enhanced updates have to-pin package compatibility and complete conventional GPUs/DSPs. HF radar chips can

been introduced. A new feature, in com- software compatibility are ensured across the be connected directly via the high-speed

parison to the first AURI generation, is an entire TC3xx family. digital radar interface.

extension of the subsystem for radar pro- The proven AURI safety concept has The improved HSM cryptographic

cessing with a signal-processing unit (SPU), been retained in principle. Safety features capability makes on-board communica-

additional memory, and optimized data path. from the TC2xx family can thus be reused, tion more secure and renders hardware

Connectivity has been significantly enhanced and the additional LBIST MBIST hardware manipulation more difficult. It integrates

with up to two Gigabit Ethernet interfaces, features in the TC3xx family eliminate the new functions to support asymmetrical

in addition to other traditional communica-

tion peripherals, and an eMMC interface for

external flash memory. Many other peripher-

als, including HSM and AD converters, have

been extended and improved.

Furthermore, AURI ’s integrated voltage

regulator supports a switch CAP DC/DC

topology in the low-end derivatives, saving

space and cost of up to two external MOS-

FETs and coils. With this topology, the power

consumption during operation can be halved.

ARCHITECTURAL EVOLUTION

With its high level of backward-compatibil-

ity, the TC xx AURI generation provides

an evolutionary path from the TC2xx

generation. This enables a fast and efficient

upgrade of designs based on the previous

generation to families with higher perfor-

mance and new features (Figure 3).

Within the same package, derivatives with

different performance levels offer high scal-

ability and flexibility. For example, all TC xx

families are available in the popular BGA-

292 package, allowing the designer to scale Figure 3: The main improvements and extensions in the TC3xx generation compared with

performance higher and lower depending on the TC2xx architecture are shown.

www.eetimes.eu | FEBRUARY 2020ww.eetimes.eu | FEBRUARY 2020www.eetimes.eu | FEBRUARY 2020

FEBRUAR w

FEBRUARY 2020 | www.eetimes.euY 2020 | www.eetimes.eu